用Verilog向ISE解释数字电路

在写Verilog程序时, 做的笔记. 主要解释与Xst的沟通过程. (一个强迫症患者和Xst警告的纠缠过程)

more ...在写Verilog程序时, 做的笔记. 主要解释与Xst的沟通过程. (一个强迫症患者和Xst警告的纠缠过程)

more ...老友的Kindle Paperwhite砖了, 据说可以连tty(UART)接口来重新来过.

more ...要设计一个低成本的软件无线电

more ...对于一个简单的软件无线电项目, 对FPGA都有哪些需求? xilinx公司的低成本FPGA: Spartan-3, Spartan-6, Artix-7, 应该如何选择?

more ...一个控制系统的开环传递函数(也有叫环路增益)决定着这个系统的性能和稳定性. 因此在线性电源这种电路中, 对其开环Bode图的仿真可以得到很清晰稳定性信息.(当然更好的是Nyquist图,但俺看不懂那图

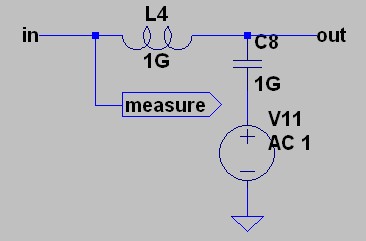

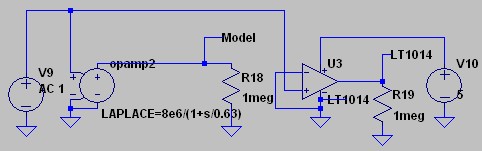

在pspice环境下仿真这个开环的图有很多方法. 可以在google搜索open loop ltspice. 我用的方法是Designing Control Loops for Linear and Switching Power Supplies 这本书推荐的方法. 就是断开环路,输入设为0,在环路中加入下图这个东西,然后用AC仿真,在measure这里测量,就可以得到结果.

我说一下我对这个电路的理解. 首先要测量的目的是要得到把环路断开, 从一端输入另一端测量输出, 来得到结果. 但如果真的是断开了环路, 则电路由于失去了DC直流的电压而工作不正常. 如会导致op输出饱和, 从而得到非线性的结果.

那么加入的电路就可以解决这个矛盾.1GH的电感起到的是AC隔离的作用, 电感在频率升高时阻抗会变高. 也就相当于断开了环路. 而1GF的电容起到的是隔离DC的作用, 使得AC信号源的DC输出不影响被测电路的DC电压.另外1G的大小可以减少负载电阻与电容的影响.

在测量时, AC输出经过1GF的电容,向右经过整个回路回到左边.

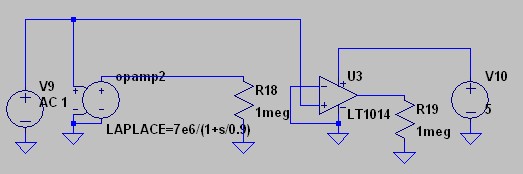

根据前一篇文章的运放模型, 简单的跟随器模型.

在这里要注意这个测量器件放的方向. R6为输出负载. 在运放正端输入被短路接到0v …

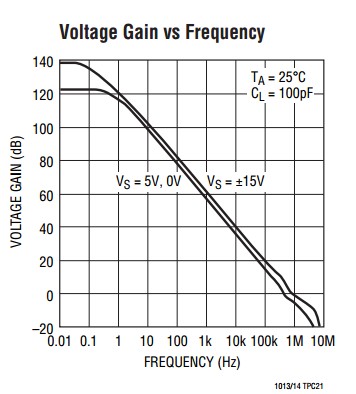

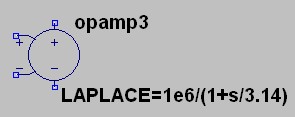

more ...运放可以被建模为一个具有低频极点和很高开环增益的压控电压源. 另外在GBP频率以上会有高频极点(不止一个).

其中, wl这个频率可以通过

这个式子计算. 注意算出来的是角频率.

如上图可以比较这个模型的精确度, 运放接成开环的模式, 输入一个AC小信号, 在输出接一个1Meg的负载电阻用来测量输出. LT1014是LT公司出的可pin to pin代替LM324的OP, 在其说明书中, LT1014的Aol在单电源5V供电,驱动100pF负载时大概是120dB.

而GBP大概是在0.5MHz左右. 则低频极点大概位于3rad/s.则模型为:

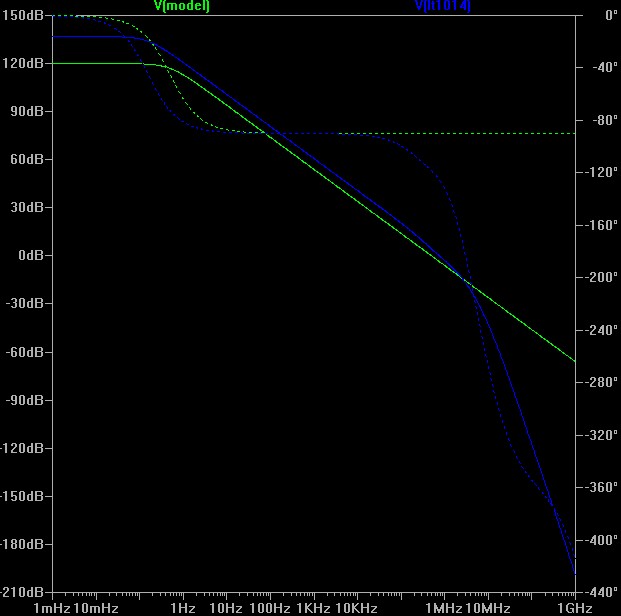

用上面的电路图仿真一下AC小信号.

可以看出以下几点:

Aol与LTSpice中的不一样, LTSpice的接近140dB.

wL位置略有不同.

在大概1MHz位置有另一个极点, 模型中没有. 在相位方面该极点从100kHz开始影响曲线.

关于第一点, 我不清楚是不是因为LTSpice中的这个spice模型没有考虑电源供电情况对性能的影响. 进而这个会影响到wL, 而高频极点我本来就没有考虑在内.

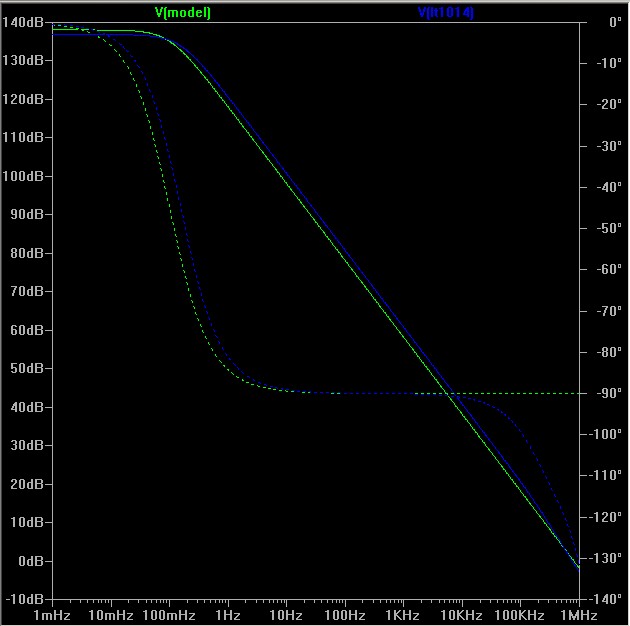

那么我们就用双15v的曲线再算一次. 其Aol大概比140dB低一点儿. 而GBP大概是0.8MHz

那么模型变为

这下就非常接近了.

more ...